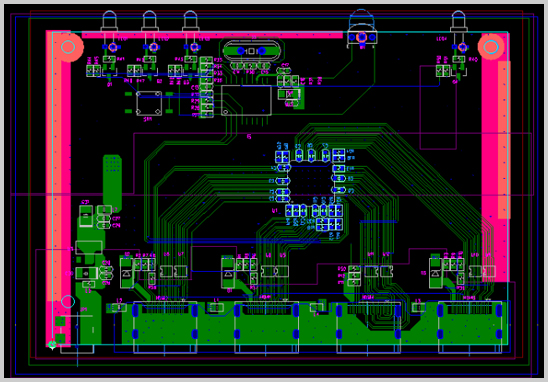

在PCB设计中,布线是将电路原理图转化为物理板上的“铜线大网”,它直接影响信号完整性、EMI/EMC表现以及可制造性。本文结合行业最佳实践,从信号、功率、高速设计以及测试可制造性等多角度,聊聊PCB布线那些不可忽视的细节。

一、布线前的准备

1. 合理元件布局

布线前先把元件按功能区分区摆放:数字、模拟、电源、接口等尽量分区,避免“信号跑断头”又拥挤。

2. 定义层叠结构

确定内层信号和电源/地平面的位置,保证关键走线旁有连续的参考平面。

二、信号完整性与串扰控制

1. 最短、最直接路径

对于普通信号线,越短越好,尽量保持直线,减少回路面积。

2. 避免平行走线

平行线间易产生串扰,若必须交叉,请垂直交叉或增加间距。

3. 分区隔离

开关电源、射频、高速数字与敏感模拟信号保持合适隔离。

三、高速信号布线要点

1. 折弯角度

避免锐角(90°),优先使用135°折弯,以减少信号反射和电磁辐射。

2. 线长匹配

时钟、差分对和总线信号要做长度匹配,确保延迟一致。

3. 阻抗控制

高速信号必须走阻抗受控线,严格按照IPC或器件手册推荐的线宽、层间距进行设置。

四、电源与地线布线

1. 回路面积最小化

开关电源走线尽量短且宽,缩小电流回路,降低EMI。

2. 地平面连续性

保持地平面完整,避免在信号线下出现断裂或分隔。

3. 去耦与铺铜

去耦电容靠近芯片VCC和GND焊盘布局,并在所在层铺大面积铜箔做参考平面。

五、差分信号与阻抗配对

1. 差分线间距与间隙

根据板厚和介电常数设置合适间距,保持特定差分阻抗(如100?Ω)。

2. 等长与同层走线

差分对应在同一层平行布线,并严格控制长度误差在?5?mils 以内。

六、过孔(Via)与线角处理

1. 过孔布局

高频信号避免频繁上下层切换;必要时使用微型埋盲孔。

2. 过孔在线上布置

如果必须在线路中放Via,建议在线路两端或信号终端附近进行阻抗补偿。

3. 折线平滑

用圆弧或多段直线代替锐折角,保证信号流畅。

七、层间布线策略

正交布线:一层水平、一层垂直,可降低层间串扰。

参考平面交替:每条信号层都应紧邻至少一个完整的参考平面。

九、可制造性(DFM)与测试性(DFT)

1. 线宽与间距

根据PCB厂工艺能力设置最小线宽与最小线距(如6?mil/6?mil)。

2. 测试点布局

在关键节点预留测试点,便于生产测试与故障排查。

3. 拼板留位

合理安排阻焊、文字和定位孔,保证批量生产顺畅。

PCB布线虽是看不见的“线路”,却承担着稳定供电、信号传输与电磁兼容的重任。只要在布线前做好布局规划,遵循最短路径、正交分层、阻抗控制、折弯优化等原则,再结合DFM/DFT要求,就能显著提升成品率和性能稳定性。宏力捷电子,多层、高精密/BGA封装及盲埋孔PCB设计专家,期待为您提供一站式PCB设计与样板服务!

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料