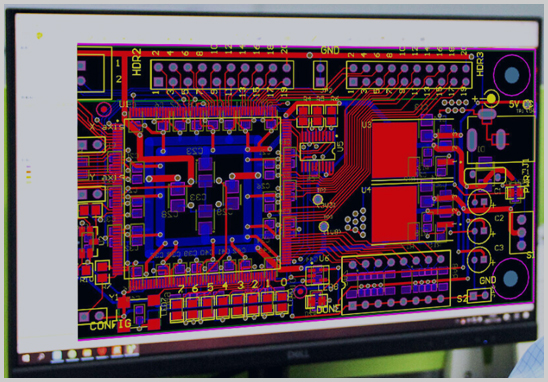

随着电子产品信号频率的提升和上升沿时间的缩短,电磁干扰(EMI)问题愈发严峻。据统计,60%的EMI问题可以通过优化高速PCB设计解决。作为专业PCB设计公司,深圳宏力捷电子深知EMI控制对产品性能和合规性的重要性,以下将详解高速PCB设计中的九大EMI规则,帮助工程师和客户高效规避风险。

高速PCB设计EMI的九大核心规则

1. 高速信号走线屏蔽规则

在高速PCB设计中,关键信号线(如时钟信号)需进行屏蔽处理,以防止电磁泄漏。若未完全屏蔽,EMI会通过信号线辐射到周围电路。

- 解决方案:在多层板中,将高速信号线布置在内层,并在其上下层铺铜接地作为屏蔽层。屏蔽线建议每1000mil打孔接地,确保屏蔽有效性。

2. 高速信号走线闭环规则

高速信号走线若形成闭环(如环形天线),会显著增强EMI辐射。例如,相邻两层信号线若平行布线且未妥善处理,可能形成闭环。

- 解决方案:避免闭环设计。若无法避免,可在闭环中添加电阻或电容破坏谐振条件,减少辐射。

3. 高速信号走线开环规则

开环走线同样会导致EMI问题,例如线形天线效应。开环区域越大,EMI辐射强度越高。

- 解决方案:优化布线路径,减小开环区域面积。蛇形走线时需遵循对称原则,避免信号反射和辐射增强。

4. 特性阻抗连续规则

高速信号在层间切换时,若特性阻抗不连续,会导致信号反射,进而增加EMI。例如,线宽或介质厚度的突变会破坏阻抗匹配。

- 解决方案:通过仿真工具计算阻抗参数,确保同层布线宽度连续,不同层阻抗匹配。使用端接电阻(如串联或并联电阻)消除反射。

5. 布线方向规则

相邻层布线方向若平行(如顶层水平、底层水平),会增加层间串扰和EMI。

- 解决方案:遵循“横平竖垂”原则,相邻层布线方向垂直,减少耦合效应。

6. 拓扑结构规则

高速PCB的拓扑结构直接影响信号完整性和EMI。例如,菊花链式拓扑适用于低频场景,而星形对称结构更适合高频设计。

- 解决方案:优先采用星形拓扑,确保信号同步性和回流路径一致性。

7. 走线长度谐振规则

若走线长度为信号波长的1/4整数倍,会产生谐振,导致EMI急剧增加。

- 解决方案:通过仿真工具分析走线长度,避免谐振条件。必要时缩短关键信号路径。

8. 回流路径规则

高速信号需有明确且最小的回流路径。回流路径面积越大,EMI辐射越强。

- 解决方案:在信号线附近布设完整的地平面,确保回流路径短且连续。

9. 器件退偶与电容摆放规则

电源噪声是EMI的重要来源。若去耦电容未合理布局,电源线可能成为辐射源。

- 解决方案:在关键器件(如CPU、DDR)附近放置高频去耦电容(0.1μF),并遵循“就近原则”。

深圳宏力捷电子的EMI解决方案

作为专业PCB设计公司,宏力捷电子提供从布局、叠层设计到EMC仿真的全流程服务:

1. 多层板设计:支持8层及以上高密度布线,优化层间隔离和阻抗控制。

2. BGA封装处理:针对高引脚器件,采用差分对布线和扇出优化,减少串扰。

3. 盲孔/埋孔技术:通过精准的孔径设计,缩短信号路径,降低EMI风险。

4. 一站式服务:客户仅需提供原理图,即可完成BOM表制作、供应商对接及样品打样。

结语

高速PCB设计的EMI控制是一项系统工程,需从布局、布线到材料选择全面优化。深圳宏力捷电子凭借丰富的行业经验和技术实力,为客户提供高效、可靠的EMI解决方案,助力电子产品通过EMC认证并提升市场竞争力。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料