利用一种创新的软件扩展增加设计验证功能,可以在

PCB设计的原理图撷取阶段实现可测试性设计(DFT)途径。

「确保设计正确」(right by design)这个概念意味着业经讨论的设计总会如预期般地顺利作业,因此,一旦设计「正确」,就不需要测试了。原则上,虽然确实如此,测试并不是发现设计缺陷的主要手段,它只是产品开发中的一个环节。

虽然在任何时候都可能出现新的「缺陷」,但在设计阶段之后出现的故障完全有可能是由制造过程引起的,特别是对于成熟的产品来说。例如,发生在波焊(wave soldering)过程中的潜在制造缺陷就可列出一长串的清单,包括:不完整的焊点、干裂或球形焊点、焊盘或阻焊剂隆起、焊盘污染、锡球;当然还有开路和焊接短路。

上述任何缺陷都可能让电路板(PCB)停摆,有些问题则可能等到交货很长一段时间后才被发现。采用「可制造性设计」(DFM)方法有助于使发生这类缺陷的可能性降至最低,这些措施一般最佳应用在PCB布局阶段。透过现代设计工具在此阶段施加一些设计规则,有助于实现DFM的自动化。

不管电路板的布局设计得多好,制造过程中的缺陷都是不可避免的,因此必须在产品出货前透过测试途径发现。采用可测试性设计(DFT)途径可以确保检测和定位出制造缺陷,即使故障发生在表面黏着元件之下。相较于严格的设计「规则」——如走线间的最小间距或在指定层上的布线,DFT途径需要更早更广泛的采用,并在原理图撷取阶段进行建置。

DFT确保设计正确

可测性设计也许比可制造性设计的主观性更强。由于受到成本、空间或复杂度的限制,对于某一项设计看似正确的方法,对另一个设计来说可能是不正确的。然而,IC制造商们几乎一致同意的是,在复杂的整合元件中包含边界扫描等DFT技术如今已经成为常态。

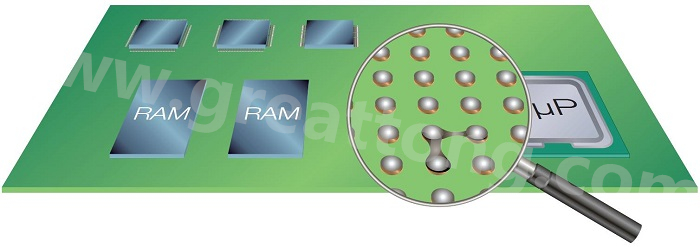

虽然JTAG经常用于除错执行于微处理器上的软件,但边界扫描具有更宽的应用范围。边界扫描的开发主要用于发现「隐藏」在先进的表面黏着元件(通常是球闸阵列或BGA元件)下方的制造缺陷。

边界扫描提供的测试存取层级明显高于其它许多测试形式,也更具成本效益,因为它「内建」于元件之中,因而不至于增加这些元件的成本。大多数的FPGA/CPLD和处理器(包括微控制器)以及一些固定功能的元件(如乙太网路收发器、介面控制器和PCI Express PHY)现在都建置了边界扫描功能。

存取一款制造产品中的边界扫描功能,必须采用合适的专业硬体和软件,并确保设计可提供这种存取是免费的;它只要求在开发的原理图撷取阶段采用DFT途径。试图在PCB布局设计期间或其后建置或校正边界扫描链是没有用的;确保在原理图撷取期间的设计正确、更加简单,因而也更具成本效益。

实现正确的设计扫描链

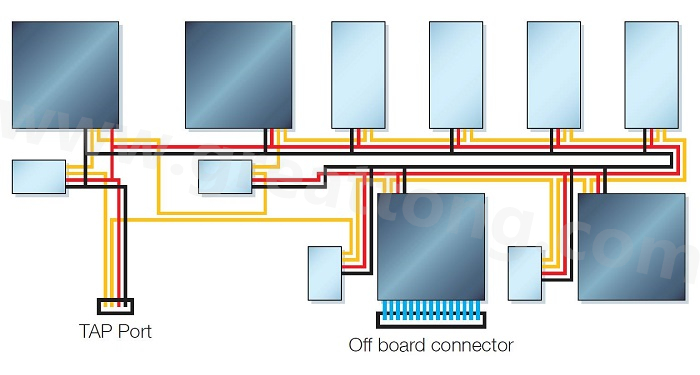

边界扫描要用专门的汇流排实现,这种汇流排由4个或5个讯号组成。这些讯号统称为测试接取埠(TAP),必须正确地连接到菊鍊配置(即扫描链)中所有具有JTAG功能的IC。TAP先从连接器布线到扫描链中的第一个IC,然后到第二个,以此类推,一直到扫描链中的最后一个IC后再回到连接器。

图1:边界扫描链依序连接PCB上具有JTAG功能的元件,从而进行测试存取以执行连接与功能测试

扫描链的顺序特性意味着边界扫描测试图案必须通过每个元件,然后返回连接器。因此,扫描链中必须毫无中断或脆弱的连接。这将带来许多DFT的考虑因素,例如确保扫描链连接到设计中每个具有JTAG介面的IC、扫描链中TAP讯号必须正确连接到这些IC的正确接脚,以及TAP讯号使用了建议的的终端连接。

除了定义TAP的电气特性,IEEE 1149.1(边界扫描)标淮还定义了扫描链的协定。这有助于辨识元件、用于TAP的接脚以及元件支援的测试功能。这些资讯储存在一个称为边界扫描描述语言档(BSDL)的专用档案中;相容JTAG的每个IC都必须有一个与之相关的BSDL档。储存在这个档案中的资讯可以让专业的软硬体供应商开发出在测试过程中用于存取和控制JTAG元件的产品。

DFT的自动化

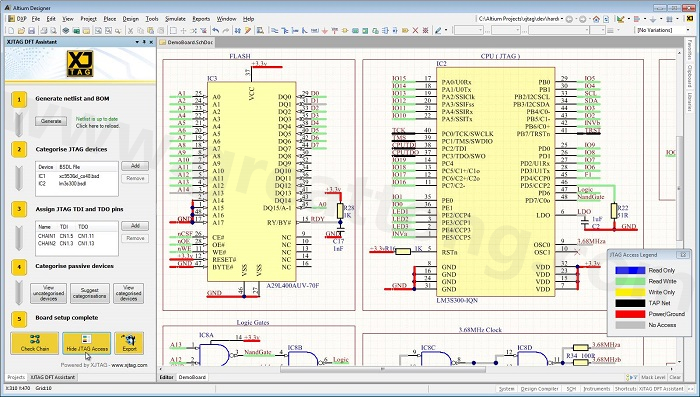

检查扫描链中所有JTAG元件是否正确连接通常是一个人为的过程,因此就像其它任何人工设计过程一样极易于发生人为错误。但最近已经能为边界扫描链实现自动化的设计验证了。藉由其边界扫描测试的专业技能,XJTAG已经为Altium Designer开发出免费的软件扩展,以辅助边界扫描链的设计验证,从而使得这个设计环境的DFT性能达到了全新的层次。

这个软件扩展被称为XJTAG DFT Assistant,它使用Altium Designer在原理图撷取阶段产生的网表,形成了扫描链如何在设计中进行连接的简图。再透过将BSDL档案导入专案中进行补充,让它理解扫描链应该如何布线。如此一来,扩展功能不仅可以检查原理图中的扫描链连接,还能显示提供给边界扫描软硬体的测试存取层级。

图2:边界扫描可以找出「隐藏」在BGA下方的制造缺陷

这一软件扩展透过两个主要的功能达到目的:XJTAG Chain Checker和XJTAG Access Viewer。所收集的资料还可以汇出,用于XJTAG的边界扫描测试开发环境XJDeveloper。因此,它可为JTAG元件和非JTAG元件支援边界扫描测试功能的开发。如果在设计时考虑边界扫描测试功能,就可以扩展测试存取到更多的电路。藉由XJTAG Access Viewer功能,设计人员可以监测、评估和儘量提高在原理撷取阶段的测试存取能力,这是在导入这种免费的软件扩展之前无法自动验证的功能。

其关键在于这种软件扩展还能够在PCB设计进入布局阶段之前,及早检测出扫描链中的错误。藉由使其成为设计过程的一部份,XJTAG DFT Assistant有助于让设计人员避免阻止扫描链作业中常见的故障,例如错误的TAP讯号布线或讯号端接不良。也许更重要的是,它能提示电路板设计人员哪些IC可以存取边界扫描测试,从而标示出应该连接的所有IC,以及哪些IC或设计区域目前无法存取边界扫描测试,但可以透过设计修改进行存取。

随着设计的进展,这些功能可以反覆使用,从而确保尽可能地利用测试存取功能,以及使边界扫描链得到正确的设计。开发人员手中掌握这些资讯不仅有助于其更加明白如何建置边界扫描,也有利于在原理图设计中实现整个DFT途径的自动化。

图3:XJTAG DFT Assistant的Access Viewer模式可以清楚地显示可用的测试存取层级,让电路板设计人员在展开PCB布局以前的原理图撷取阶段尽可能地提高测试存取能力

了解边界扫描和BSDL档案有助于像XJTAG等业者开发出从原型到量产的整个产品生命周期中都必须使用边界扫描功能的软硬体产品。利用这种专业知识为Altium Designer开发免费的扩展软件,开发人员现在可以存取功能强大的设计验证技术,大幅提高第一次就成功的开发能力。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料