为了提高传输速率和传输距离,电脑和通讯产业正逐步转移到高速串列汇流排,在晶片-晶片、板卡-板卡与背板间实现高速互连。这些高速串列汇流排的速率正从过去USB2.0、LVDS及FireWire1394的几百Mbps,提升到当前PCI-Express G1/G2、SATA G1/G2、XAUI/2XAUI、XFI的数Gbps,甚至达10Gbps,这意味着电脑与通讯业的PCB厂商对差分走线的阻抗控制要求将越来越高,因此使

PCB制造商及

高速PCB设计人员面临前所未有的挑战。本文将结合PCB业界的测试标淮IPC-TM-650手册,讨论真实差分TDR测试方法的原理及特点。

IPC-TM-650测试手册是一套全面性PCB产业测试规格,从PCB的机械特性、化学特性、物理特性、电气特性、环境特性等方面提供了详尽测试方法及测试要求。该手册的2.5节描述了PCB电气特性,而其中的2.5.5.7a则全面介绍了PCB特征阻抗测试方法和相应的测试仪器要求,并包含了单端走线和差分走线的阻抗测试。

TDR基本原理

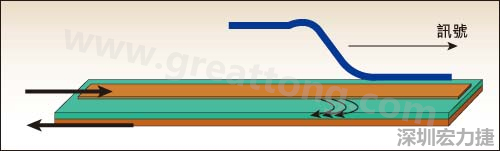

图1是一个阶跃讯号在传输线(如PCB走线)上传输时的示意图。而传输线是透过电介质与GND分隔的,就像无数个微小的电容器并联。当电讯号到达某个位置时,就会使该位置上的电压产生变化,如同为电容器充电。由于传输线在此位置上具备对地电流迴路,因此会产生阻抗。但该阻抗只有阶跃讯号自身才能感觉到,这就是所谓的特征阻抗。

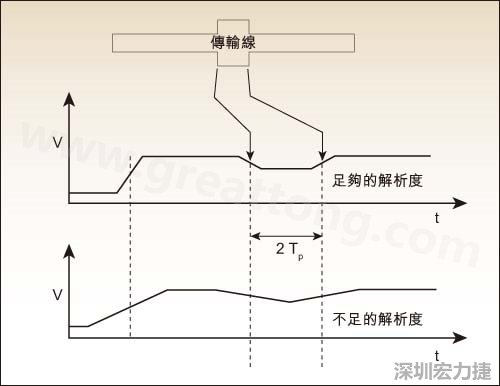

当传输线上出现阻抗不连续的现象时,在阻抗变化之处的阶跃讯号就会产生反射现象,若对反射讯号进行取样并显示在示波器屏幕上,就会得到图2所示的波形,该波形显示了一条被测试的传输线在不同位置上的阻抗变化。

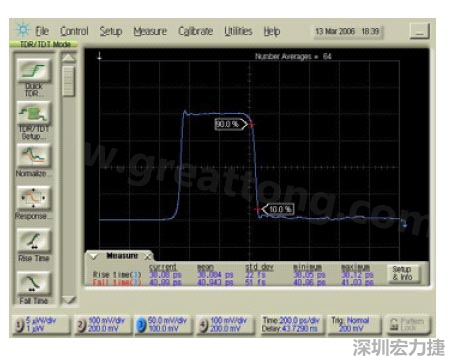

我们可以比较图2中的两个波形。这是使用两台解析度不同的TDR设备在测试同一条传输线时获得的测试结果。两款设备对传输线阻抗变化的反映不同,一个明显而另一个不明显。TDR设备感测传输线阻抗不连续的解析度主要取决于TDR设备发出之阶跃讯号上升时间的快慢,快的上升时间可获得高解析度。而TDR设备的上升时间往往和测试系统的频宽相关,频宽高的测试系统拥有更快的上升时间。从另一个角度考虑,TDR设备的系统频宽限制了TDR测试的解析度。在IPC-TM-650测试手册中,对TDR设备的上升时间是依照系统上升时间(tsys)来定义。在测量一台TDR设备的系统上升时间时,可以让一台TDR设备的输出短路,此时可测出该TDR设备的(tsys)(上升及下降时间)。图3的TDR设备系统上升时间约为28ps。

图1:阶跃讯号在传输线中的传输情况

图2:TDR测试反映传输线的阻抗资讯

图3:TDR系统上升/下降时间的测定

图4是另一台TDR设备的系统上升/下降时间测试结果,约在38ps~40ps之间。这代表不同的TDR设备在系统上升/下降时间上有很大区别,因此其呈现的传输线阻抗测试解析度也有很大不同。

图4:另一台TDR设备的上升/下降时间测量结果

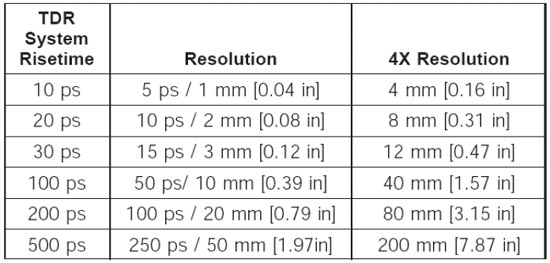

系统上升时间和解析度的关系可用下列公式表示:

Resolution= (tsys*V)/2,V为电讯号在被测试传输线上的传输速率。

为方便测试者瞭解TDR测试解析度及PCB走线的最小测试长度,IPC-TM-650测试手册也提供了速查数据(图5)。

图5:IPC-TM-650测试手册提供的对照表

差分TDR设备基本要求

在以往的IPC-TM-650手册中,对PCB差分TDR测试的要求较为宽松。手册中允许测试者根据TDR测试设备的情况使用两种不同的方法。

方法一:当测试者拥有差分TDR测试设备时,测试设备同时打出两个幅度相等、方向相反的阶跃脉冲,并透过这对差分讯号的相互作用直接测出差分走线阻抗。

方法二:当测试者没有差分TDR测试设备时,测试设备在差分走线(A线与B线)时,先在A线上打出阶跃讯号,测试A阶跃讯号在A线上的反射特性记为AA,同时测出A阶跃讯号在B线上的感应讯号,记录为BA。随后,在B线上打出阶跃讯号,测试B阶跃讯号在B线上的反射特性记为BB,同时测出B阶跃讯号在A线上的感应讯号,记录为AB。透过对获得的AA、AB、BB、BA四个数值进行计算,可得出差分走线阻抗。该方法又称为‘伪差分(Super-Position)’。

但是在目前的最新版IPC-TM-650手册中,仅仅保留了方法一中的真差分TDR测试描述。而不再有方法二的‘伪差分’TDR测试方法描述。以下将就两种差分TDR测试方法进行对比。

1. 真差分测试法

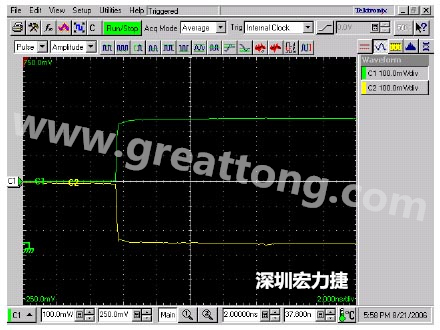

如图6所示:阶跃讯号A和阶跃讯号B是一对方向相反、幅度相等且同时发出的差分阶跃讯号。我们不但在差分TDR设备上看到差分的阶跃讯号,当使用一台即时示波器观测这对阶跃讯号时,也能证实这是真正的差分讯号。

图6:真实差分TDR测试系统显示的波形

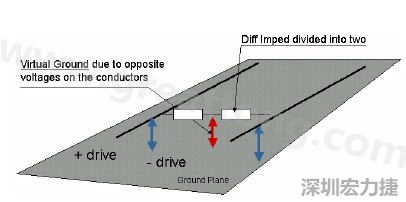

由于注入DUT(待测设备)中的TDR阶跃脉冲是差分讯号,因此TDR设备可以直接测出差分走线的特征阻抗。使用差分阶跃讯号进行真差分TDR测试,为使用者带来的最大好处就是可以实现虚拟接地,如图7所示。

图7:虚拟接地原理

由于差分走线和差分讯号是平衡的,差分讯号的中心电压点和地平面是等电势的,因此在使用差分阶跃讯号进行差分TDR测试时,只要保证通道A和通道B共地,即无需与DUT之间接地。

2. 伪差分法

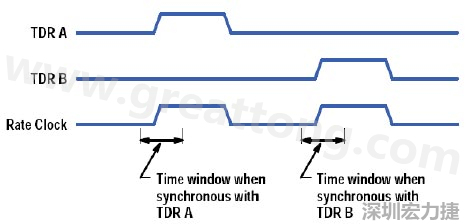

如图8所示,阶跃讯号A和阶跃讯号B并非同时打出,且方向不是相反,因此注入到DUT中的阶跃讯号完全不是差分讯号。

图8:伪差分法TDR测试原理

在这种‘伪差分TDR’设备屏幕上,往往会经过人为的软体调整,让我们看到同时发出且方向相反的阶跃讯号。

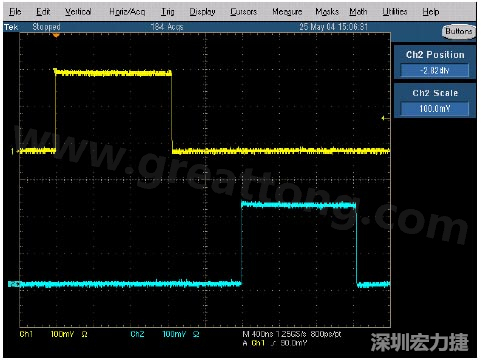

但若用一台即时示波器来观测这两个阶跃脉冲,则可看到如图9所示的波形,可看出两个阶跃脉冲间的真实即时关系中存在着2us的时间差,即这两个阶跃讯号并不是差分讯号。

图9:用即时示波器观察‘伪差分’法TDR系统波形

这种TDR阶跃脉冲称为伪差分讯号,因为它并没有真正实现一个高速差分讯号的传输过程,即幅度相等,方向相反。因此这种方法不能直接测出DUT的差分阻抗,只能使用软体计算方法对差分阻抗测试进行模拟运算。在TDR设备上得到经过运算的2个幅度相等,极性相反阶跃脉冲。这种差分TDR测试带来的侷限性是:无法真实获得差分讯号间的同时相互作用、无法实现虚拟接地;且当进行差分TDR测试时,通道A和通道B的探棒都必须有各自独立的接地点。但在PCB内部的真实差分走线附近往往找不到接地点,导致无法在PCB内部对真实的差分走线进行测量。

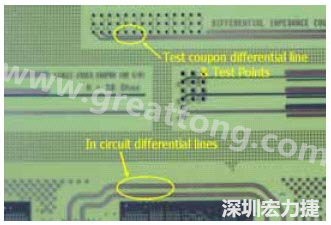

为解决伪差分TDR设备难以实现对PCB内部真实走线进行差分TDR测量的问题,一般的PCB生产商都会在PCB周围加上具有接地点的差分走线测试条,称为‘Coupon’,图10为典型的PCB,上方是测试用‘Coupon’,下方是板内的真实走线。为方便探棒连接,测试点的间距通常达100mil (2.54mm),已大幅超越差分走线间距;测试点旁边还会放置接地点,间距同样为100mil。

图10:电路板上Coupon与真实走线的差别

Coupon测试的侷限性与差异

从图10中可看到测试‘coupon’和板内真实走线间的差别:

1. 虽然走线间距、走线宽度一致,但coupon测试点的间距固定为100mil(即最初的双列直插式IC接脚间距),而板内真实走线的末端(即晶片接脚)间距是不同的,随着QFP、PLCC、BGA封装的出现,晶片接脚间距远小于双列直插式IC封装间距。

2. coupon走线是理想的直线,而板内真实走线往往是弯曲的。PCB设计人员和生产人员很容易将coupon的走线理想化,但PCB上的真实走线则会因为各种因素导致走线不规则。

3. coupon与板内真实走线在整个PCB上的位置不同。coupon都位于PCB边缘,在PCB出厂时往往会被生产商去掉。而板内真实走线的位置则相当多样,有的靠近电路板边缘,有的位于板中央。

由于上述差异,导致coupon的特征阻抗往往与板内真实走线阻抗存在几项差异。首先是coupon测试点间距与coupon走线的间距不同,导致测试点与走线之间的阻抗不连续。而PCB内的真实差分走线末端(即晶片接脚)间距往往与走线间距相等或非常相近,因此会带来不同的阻抗测试结果。

其次是弯曲的走线与理想走线反映的阻抗变化不一致。在走线弯折处的特征阻抗往往不连续,而coupon的理想化走线则不能反映由于走线弯曲所带来的阻抗不连续现象。

第三是coupon与真实走线在PCB上的位置不同。目前的PCB均采多层走线设计,在生产时需经过压制。当PCB压制时,电路板上的不同位置所受到的压力也不可能一致,如此将导致PCB不同位置上的介电常数不同,特征阻抗也当然不同。

由此可见,仅对PCB的coupon进行TDR测试并不能完全反映PCB内真实走线的特征阻抗。无论是PCB生产商、高速电路设计人员或制造者,都希望能对PCB内的真实高速差分走线直接进行TDR测试,以获得淮确的特征阻抗资讯。阻碍真实测试的主要原因有两项:难以找到差分TDR探棒的接地点;以及差分走线的末端间距是多变的。

差分TDR测试优势

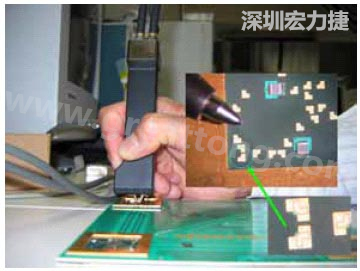

如果TDR设备发出的阶跃讯号是差分讯号,就可以实现虚拟接地,即差分TDR探棒无需与被测试的PCB接地。只要测试者手中有一个间距可调的差分TDR探棒即可完成测试。

图11是一个频宽达18GHz的差分TDR探棒在进行差分TDR测试时的情况。它的探针间距可在0.5mm~4.5mm间连续可调,即使在测试一个比圆珠笔尖还微小的测试点时,仍能让设计人员以单手完成作业。

图11:高频宽差分TDR探棒进行精密的TDR探测

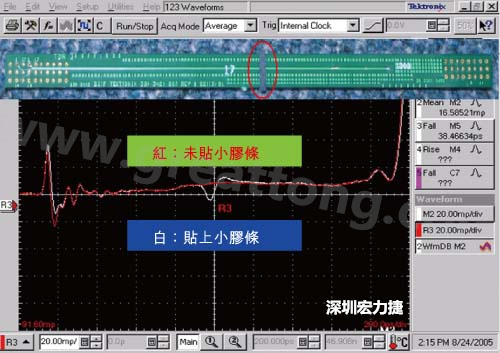

由于探棒频宽达18GHz,因此可获得很高的测试解析度,图12是对coupon差分走线进行测试时获得的结果。红色波形是对coupon最初的测试结果,随后在走线上贴上了一个很小的胶条(红色圆圈所示部位)然后再进行测试,获得了如白色波形的测试结果,显示出仅贴上小胶条所带来的微小阻抗不连续也能透过高频宽差分TDR探棒清晰地反映出来。

图12:高频宽TDR差分探棒进行PCB差分探测获得的结果

真实差分的TDR设备配合高频宽差分探棒进行PCB差分特征阻抗测试时,无需在PCB内辛苦地寻找接地点,只要探针调整到合适的间距,即可轻松对PCB内的真实差分走线进行探测。

本文小结

使用一台真实差分的TDR设备,并利用差分讯号可实现虚拟接地的便利性,再搭配间距可调的差分TDR探棒,将能轻松实现对PCB内真实差分走线的特征阻抗测量,让

高速PCB设计人员和PCB制造商在进行PCB测试时获得极高的测试效率和淮确的测试结果。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料