随着

电路板设计日趋复杂,开始将现有的硬件/电源管理架构性能推向极限。目前最常用的电路板管理架构共有四种,虽然都可用于支援这些复杂的设计,但是或多或少都需要在设计的可扩展性、工作量或成本方面做出让步或妥协。

最近,第五种电路板管理架构出现了,它能够提供目前最高的性能、安全性和灵活性,同时大幅减少设计工作量和建置成本。本文将探讨这种全新的架构,主要着重于其提供的电源管理功能。

概述

我们通常将一块电路板分为两个功能模组(图1)——负载管理(Payload Management)和硬件管理(Hardware Management)。对于大多数的电路板来说,负载功能部份占整个电路板面积的80%至90%(资料/控制层和/或处理器)。剩下的10%至20%则为硬件管理部份,用于执行硬件级的监控/控制或内务处理。

图1:在典型的电子系统中,硬件管理部份通常占电路板面积的10%~20%

遗憾的是,目前大多数硬件管理解决方案很难进行扩展以满足越来越复杂的负载功能需求。例如,尽管硬件管理部份仅占电路板面积的10%至20%,但这部份的设计和除错所需的时间占整个开发周期相当大的比重(30%至40%)。同样地,硬件管理器占用总材料成本(BOM)的比重也高得不成比例。

直到最近,一种全新的分散式架构面世了,它比其他架构更具有可扩展性,而且能以更低的BOM成本实现。为了便于瞭解分散式架构的优点,我们先讨论最常用的四种硬件管理架构(图2-5)如何建置电源管理功能,接着再深入探索分散式架构(图7)。

基于控制PLD的电源管理架构比较

以下将就四款常用的电源管理架构进行比较(图2-5)。

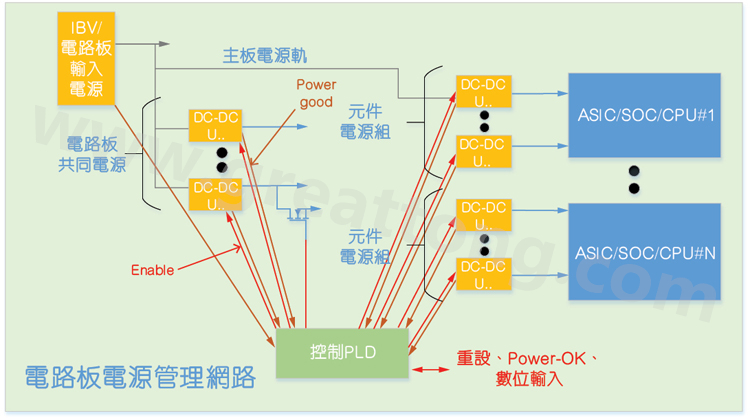

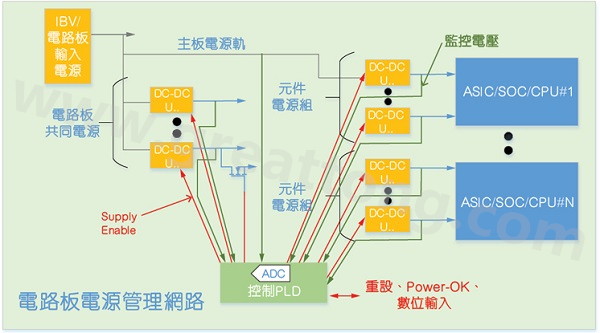

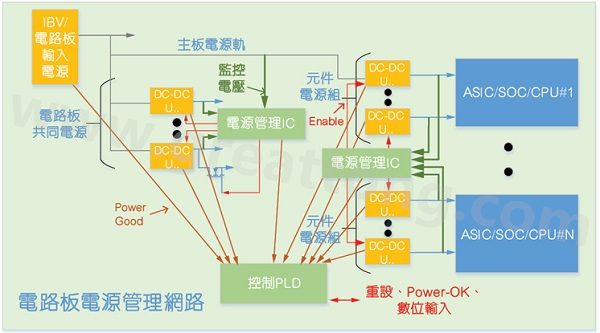

电源架构#1:基于CPLD的电源管理和内务处理

在这种架构中,电源管理功能被添加到板上控制PLD (CPLD)中。该CPLD监控输入电源和每个DC-DC转换器的‘Power Good’讯号(图2)。使用CPLD实现时序演算法产生‘Enable’讯号用于负载电路上电,避免导致损坏或逻辑错误。该CPLD还可产生逻辑讯号,如重设(Reset)和Power Good等讯号,以确保负载元件能够在上电时开始操作或在断电时停止操作。它还负责产生序列,以便在断电或侦测到故障时安全地停用电源。PLD易于支援事件导向的解决方案,可为不同的故障组合分别提供响应。

图2:基于CPLD的硬件管理系统,可实现电源管理和内务处理功能

图2:基于CPLD的硬件管理系统,可实现电源管理和内务处理功能

对于这类型的设计,所有的电源时序、保护和控制功能均使用CPLD实现,通常以VHDL或Verilog编写。

优点:

? 低成本

? 直观的架构,使得CPLD的时序逻辑易于因应新应用进行调整

? 使用一种设计环境(常用Verilog)即可实现设计

? 事件导向的架构能以灵活的方式对各种故障做出不同的回应

缺点:

? 由于每个电源需要2条讯号通道,更大、更复杂的设计开始面临更多CPLD I/O埠数以及电路板拥挤的挑战

? Power Good侦测不精确(通常为8%到20%的错误率)以及无法监控电源电压的趋势,导致可靠性降低

? 添加自动测量功能(监控实际的电源电压,而非Power Good讯号),必须添加1个A/D转换器,增加了电路板的成本和复杂度

? 需要电路板级工程师(具备数位电路经验)建置所需的功能,在很多情况下,这一类的工程师并不是电源方面的专家

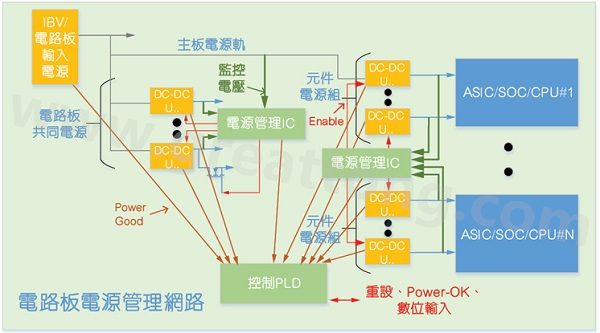

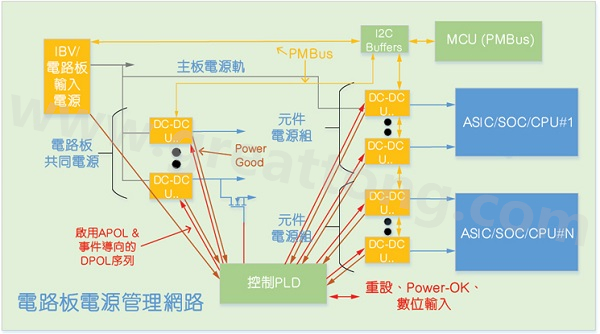

电源架构#2:采用电源管理IC置电源管理,并使用CPLD进行内务处理

在此功能拆分的架构中,1颗电源管理IC负责为电路板的DC-DC转换器进行监控和定序(图3)。因为电源管理IC能直接监控电源的电压,还可执行微调和裕度功能。CPLD使用电源的Power Good状态来产生必要的控制、状态和内务处理讯号。

图3:使用电源管理IC和CPLD实现的硬件管理系统

图3:使用电源管理IC和CPLD实现的硬件管理系统

这些设计经常使用基于GUI配置的工具来定义电源管理IC功能,而CPLD逻辑则使用VHDL或Verilog加以定义。

优点:

? 减少CPLD的I/O数量,因为‘Enable’功能可由电源管理IC执行

? 电路板空间更宽裕,得以实现更简化的布局和更少的PCB层数

? 藉由直接监控电源电压,电源管理IC可取得更加精确的系统整体健康资讯,提高系统稳定度

缺点:

? 电源管理IC增加了BOM成本——特别是需要多个元件时

? 该架构可提供事件导向的响应,但是如果部署了两个以上的电源管理IC就会增加设计复杂度

? 为更复杂的设计调整序列将变得更困难——特别是当牵涉到为多个电源管理IC划分功能时

? 由于设计流程必须使用多个工具(GUI + VHDL/Verilog),可能需要多名工程师,而且会增加设计风险

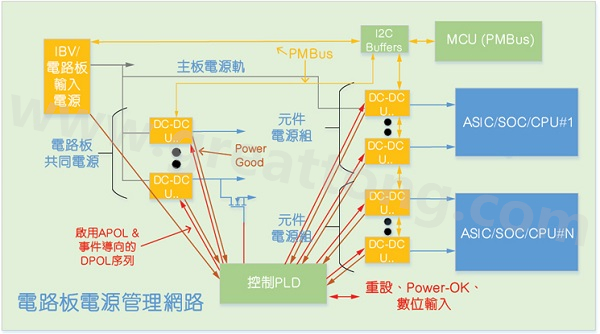

电源架构#3:使用CPLD实现内务处理,并以PMBus实现基于MCU的电源管理功能

图4中的架构使用微控制器(MCU)来控制数控负载点(DPOL)的电源时序。MCU使用电源管理汇流排(PMBus)来管理DPOL——PMBus是基于I2C汇流排的双线通讯协定。CPLD负责板上内务处理功能以及控制带有类比控制介面(APOL)的任意负载点DC-DC转换器。为了简化软件设计,大多数基于MCU的电源管理设计采用时间序列方案。

图4:使用CPLD和MCU共同实现的硬件管理系统

图4:使用CPLD和MCU共同实现的硬件管理系统

基于软件的电源管理存在另一个潜在缺点,即需要更长的故障回应时间(通常需要10~15毫秒,而CPLD的回应时间则是微秒级的)。对于需要更快回应时间(或者是事件导向的序列)的某些故障来说,可添加CPLD作为第二道保护措施。

实现基于软件的电源管理需要用于MCU的软件和CPLD设计的VHDL或Verilog。

优点:

? 设计十分易于进行调整(仅针对基于时间的序列)

? 丰富的软件开发工具,使得基于MCU的解决方案能够更快、更方便地进行除错。

? 升级韧体即可快速更改设计

? 简化PCB设计——DPOL周围的布线更有馀裕

缺点:

? 更昂贵的BOM成本

? 难以针对事件导向的序列需求调整设计

? 需要多种设计工具(Verilog/VHDL+软件)

? APOL和DPOL混合控制解决方案存在以下多项缺点:(1)较难模拟(2)硬件管理功能仅能在原型板开发环境中进行测试(3)复杂度增加了系统除错时间

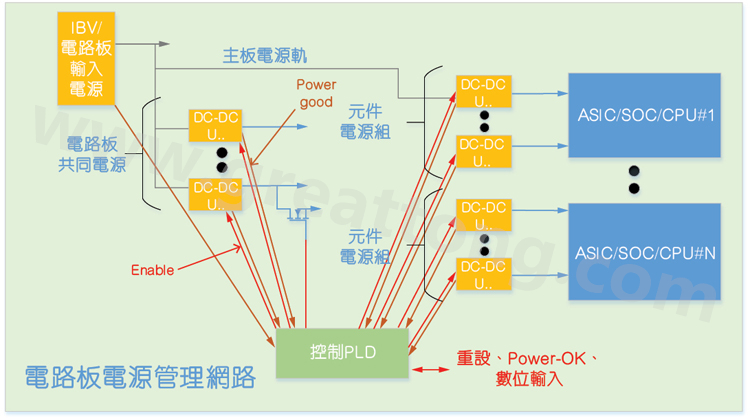

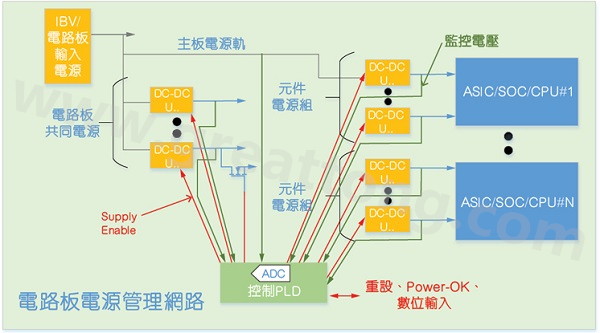

电源架构#4:使用CPLD与晶片上ADC实现电源管理和内务处理

为了克服Power-Good讯号不精确导致的问题,可使用配备晶片上类比数位转换器(ADC)的CPLD来监控板级电源电压。在此架构中,CPLD建置使用晶片软/硬处理器核心的电源管理功能,而内务处理功能则由硬件逻辑实现(图5)。

图5:使用配备晶片上ADC的CPLD实现硬件管理系统

图5:使用配备晶片上ADC的CPLD实现硬件管理系统

针对这种类型的设计,设计工程师常常以软件开发电源管理功能,以及使用VHDL/ Verilog开发其他内务处理功能。

优点:

? 该解决方案十分易于进行调整或搭配其他设计

? 结合电源管理和内务处理功能,缩短设计时间

? 该架构可为远端系统管理器提供电压遥测功能

缺点:

? 需要更高密度与I/O接脚数更多的CPLD

? 复杂的CPLD增加系统成本

? 将低电压类比遥测布线至单一位置,将使电路板空间更加拥挤

? 迫使数位电路工程师必须同时建置电源管理功能以及数位控制功能

分散式电源管理架构

上述的每一种解决方案都会使得相关设计做出不同程度的妥协,以在性能、灵活性、安全性、成本、复杂程度以及便捷性之间取得平衡。

随着电源管理系统变得越来越大和越来越复杂,要做出上述妥协也变得越来越困难。而下文介绍的分散式电源管理架构由于使用了低成本的类比感测与控制(ASC)电源管理元件,避免了上述其他架构在设计方面的许多让步。这些ASC元件可实现完整的硬件管理功能(电源和温度管理、控制通道以及内务处理功能,被统一称作硬件管理功能)。

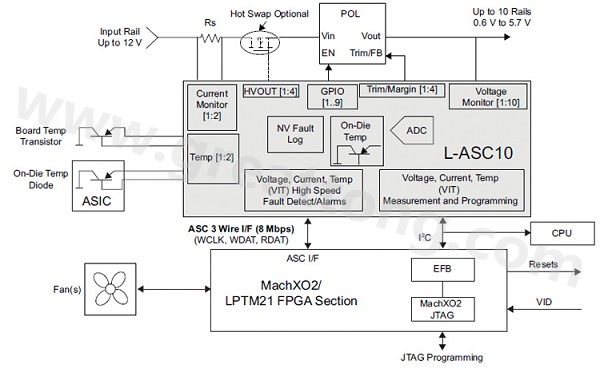

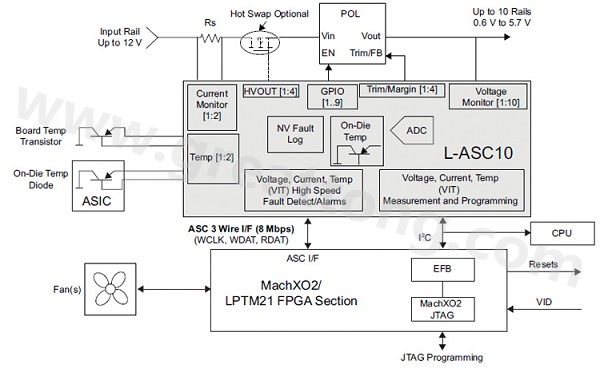

例如,莱迪思半导体(Lattice Semiconductor)的L-ASC10是一款硬件管理(电源、温度和控制层)扩展器。它可与CPLD(如莱迪思的低成本MachXO2系列)配合使用,以实现电路板的硬件管理功能。图6显示硬件管理功能如何在L-ASC10及其辅助晶片MachXO2CPLD之间进行划分。

图6:L-ASC10远端感测和控制元件

图6:L-ASC10远端感测和控制元件

每一条类比感测通道都可透过两个独立的可程式比较器进行监控,支援高/低以及输入/输出(视窗比较)监控功能。ASC和CPLD之间的通讯则透过一条3线序列汇流排(Tx/Rx/Ck)实现。

接下来,我们将会看到使用单条序列汇流排监控多个电源电压时,可大幅降低PLD所需的I/O数量。

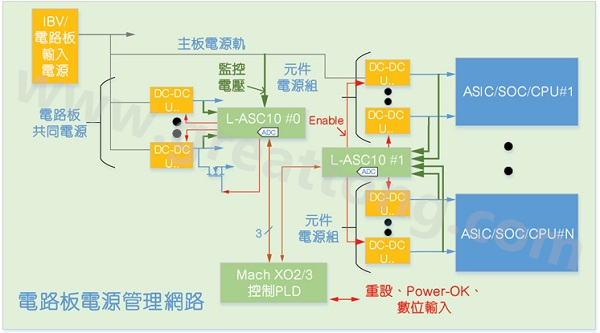

电源架构#5:由CPLD和ASC元件(提供分散式电压感测和控制)实现的电源管理和内务处理功能

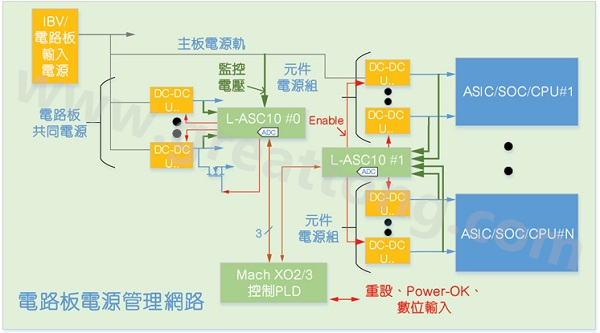

在分散式硬件管理架构中,CPLD使用几个外部ASC元件监控电源电压,并传输‘Enable/Disable’指令至DC-DC电源,并执行其他内务处理功能。

图7:使用分散式架构实现的硬件管理系统

图7:使用分散式架构实现的硬件管理系统

电源管理和内部处理功能均可使用GUI工具、VHDL/Verilog或结合上述两者实现。

优点:

? 常见的3线汇流排最大程度减少所需的CPLD I/O接脚数

? 简化的PCB布线,大幅提升电路板馀裕

? 整个系统可采用一种设计环境(GUI或VHDL/Verilog)进行开发

? 分散式架构是高度可扩展的

? 电压、电流和温度监控功能整合于ASC元件中,降低解决方案成本

? 整合电源管理和内部处理功能,缩短设计时程

? 采用莱迪思的标淮电源除错套件,大幅缩短电路板除错时间

总结

随着电路板级系统的设计复杂度日益提高,硬件管理系统在设计工作量和BOM成本这两方面所占的比重越来越大。使用CPLD和POL电源实现某些或所有的管理功能,可减轻上述趋势带来的困难,然而此时成本变成了拦路虎。现在,分散式硬件管理架构面世了,可透过3线序列链路将CPLD连接到低成本的感测元件。除了降低设计复杂度、电路板空间要求以及BOM成本之外,该架构还可使用多种类比和数位工程师常用的工具进行建置。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料