为PCB设计降低EMI的最佳方法之一就是灵活地使用运算放大器。遗憾的是,在许多应用中,运算放大器用于降低EMI的这个作用通常被忽略了...

汽车、工业、医疗和许多其它应用经常会用到一些敏感的类比电路,这些电路在其工作环境中必须执行其功能,同时保持不受杂讯干扰的影响。这些干扰中有许多是来自同一印刷电路板(PCB)上的其他「杂讯」电路,同时,藕合杂讯至PCB及其电路的线缆也会引发其它干扰。

为PCB设计降低电磁干扰(EMI)的最佳方法之一就是灵活地使用运算放大器(OP Amp)。遗憾的是,在许多应用中,运算放大器用于降低EMI的这个作用通常被忽略了。这可能是源于「运算放大器易受EMI的影响,而且必须采取更多措施来增强对杂讯的抗干扰能力」这样的成见。尽管许多以前生产的元件确实是这样,但设计师可能没意识到,最近的运算放大器通常具有比前几世代更好的抗干扰性能。设计师也可能不了解或没考虑到运算放大器电路可以为系统和PCB设计降低杂讯所提供的关键优势。本文回顾EMI的来源,并讨论有助于为敏感PCB设计减缓近场EMI的运算放大器特性。

EMI的来源、受扰电路和藕合机制

EMI是由电气杂讯的来源引起的干扰,这种杂讯源通常是无意且非期望的。在各种情况下,干扰的杂讯讯号都是电压、电流、电磁辐射这三者之一,或杂讯源以这三种形态的某种组合藕合至受扰电路。

EMI并不限于射频干扰(RFI)。「较低」频率范围内低于射频的频段存在强大的EMI源,如开关稳压器、LED电路以及作业于几十到几百KHz范围的马达驱动器。60Hz线路杂讯则是另一个例子。杂讯源经由四种藕合机制中的一种或多种,将杂讯传递到受扰电路。这四种方式中的三种被认为是近场藕合,包括传导藕合、电场藕合和磁场藕合。第四种机制是远场辐射藕合,其中电磁能量可在多种波长上辐射。

主动滤波差动模式杂讯

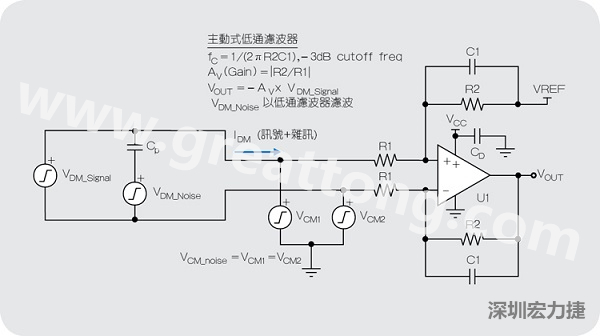

主动式运算放大器滤波器可以在电路频宽内显著降低PCB上的EMI和杂讯,但在许多设计中并未被充份利用。期望的差动模式(DM)讯号能以频带限制,而不需要的DM杂讯则可加以滤除。图1显示通过寄生电容(CP)藕合到输入讯号中的DM杂讯。组合讯号和杂讯由一阶主动低通滤波器接收。差分运算放大器电路的低通截止频率被设置为仅高于R2和C1所需的讯号频宽。

较高的频率以20dB/decade的幅度衰减。如果需要更大的衰减,则可以使用更高阶的主动式滤波器(例如-40或-60dB/decade)。推荐使用<1%容差的电阻。同样地,具有极佳温度系数(NPO、COG)和5%(或<5%)容差的电容器可获得最佳的滤波器性能。

图1:DM和CM输入杂讯施加于主动式运算放大器滤波器

降低输入共模杂讯

在图1中,共模(CM)杂讯源也在电路输入端产生杂讯。CM杂讯可被形容为在两个运算放大器输入端共有(或相同)的杂讯电压,而且不是运算放大器试图测量或调节的一部份预期DM讯号。CM杂讯能以多种方式发生。其中一例是在一个系统中,电路的接地参考电压与其连接的第二个电路处于不同的电压电位。「接地」电压的差异可以是毫伏(mV)级或若干伏(V)的程度,而且还可能发生在许多不同的频率范围。电压的这些差异会导致意外的压降,并且可能干扰连接电路的电流流动。内建许多电路的汽车、飞机和大型建筑物通常易于受到这种类型的干扰。

运算放大器的一个重要优势在于其差分输入级架构,以及在配置为差分放大器时抑制CM杂讯的能力。虽然可为每个运算放大器指定共模抑制比(CMRR),但电路的总CMRR还必须包括输入和回馈电阻的影响。电阻变化强烈影响CMRR。因此,具有0.1%、0.01%或更佳容差的匹配电阻,才能实现应用所需的CMRR。虽然使用外部电阻可以实现良好的性能,但使用具有内部微调电阻的仪器或差分放大器也是另一种选择。例如INA188是具有内部微调电阻和104dB CMRR的仪表放大器。

图1中,如果杂讯在电路的有效频宽内,则CM杂讯(VCM_noise=VCM1=VCM2)可被运算放大器电路的CMRR所抑制。抑制等级取决于R2/R1选择的精确匹配电阻。公式1可用于确定CMRRTOTAL,它包括资料手册中规定的电阻容差(RTOL)和运算放大器CMRR的影响。例如,如果运算放大器资料手册指定其CMRR(dB)= 90dB,则(1/CMRRAMP)= 0.00003。在许多电路中,电阻容差将会成为实现目标CMRRTOTAL的主要限制因素。

方程式1是从理想运算放大器的CMRR等式中汇出,其中CMRRAMP被假定为非常大(无穷大)。对于理想的运算放大器,(1/CMRRAMP)为零,CMRRTOTAL仅由电阻和AV确定。CMRRTOTAL可用公式2转换为dB。

公式(1):

公式(2):

其中,AV=运算放大器的闭路增益,RTOL=R1和R2的容差%(例如0.1%、0.01%、0.001%),CMRRAMP=资料表规格中以十进位格式表示的CMRR(不是dB)。

提高对RFI和其它高频EMI的抗干扰度

如前所述,主动式滤波和CMRR能可靠地降低元件频带限制范围内的电路杂讯,包括高达MHz范围的DM和CM EMI。然而,暴露在高于预期工作频率范围的RFI杂讯可能会导致元件的非线性行为。运算放大器在其高阻抗差分输入级最易受RFI影响,因为DM和CM RFI杂讯可由内部二极体(由硅上的p-n结形成)整流。整流后产生一个小的直流(DC)电压或偏移,被放大并可能在输出端表现为错误的DC偏移。根据系统的精确度和灵敏度,这可能会产生不良的电路性能或行为。

所幸使用两种方法之一可提高运算放大器对RFI的抗干扰能力(或降低敏感度)。第一种也是最好的选择是使用EMI硬化(EMI-hardened)的运算放大器,它包括内部输入滤波器,可以抑制数十MHz至高达GHz范围内的杂讯。TI目前提供80多种EMI硬化元件,可透过TI运算放大器参数搜寻引擎寻找「EMI硬化」。

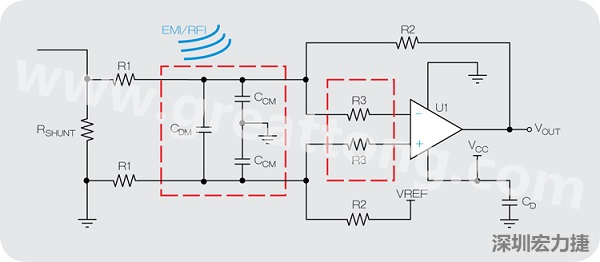

第二个选择是将外部EMI/RFI滤波器添加到运算放大器的输入。如果设计只需要使用不包括内部EMI滤波器的元件,这可能是唯一选择。图2显示使用外部DM和CM滤波器的标淮差分放大器配置,针对的是更高的EMI频率。

图2:被动式EMI/RFI输入滤波器提高了高频抗扰度

如果没有输入滤波器,电路增益为|R2/R1|。如果添加了被动式输入滤波器,通常需要R3电阻来防范CDM电容降低放大器的相位裕度。DM低通滤波器由R1电阻、CDM和两个CCM电容组成。CM低通滤波器使用R1电阻和两个CCM电容。

DM和CM滤波器(fC_DM和fC_CM)的-3dB截止频率的等式如下所示。fC_DM设置为运算放大器电路的期望频宽以上频率,而且通常先确定CDM。然后再选择比CDM更小至少十倍的CCM电容,以便使其对fC_DM的影响降至最低,而且也因为CCM电容针对的是较高频率。所以,fC_CM将被设置为高于fC_DM的频率。请注意,EMI硬化元件可用于取代红色线框所包围的元件,简化了设计。

公式(3):

公式(4):

低输出阻抗降低干扰

运算放大器的另一个重要特性是其极低的输出阻抗,在大多数配置中通常为几欧姆(Ω)或更小。要了解如何有益于降低EMI,必须先考虑EMI如何影响低阻抗和高阻抗电路。

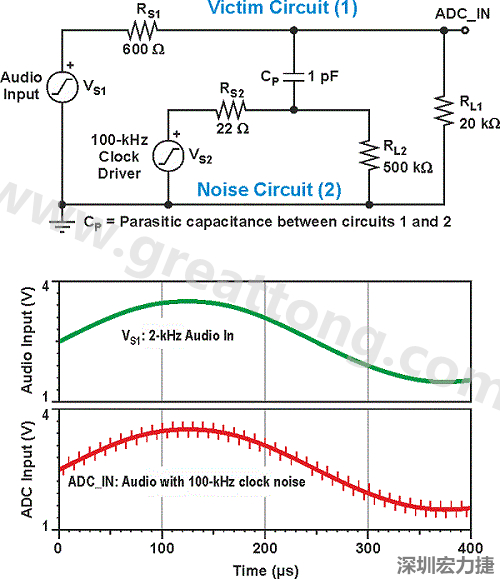

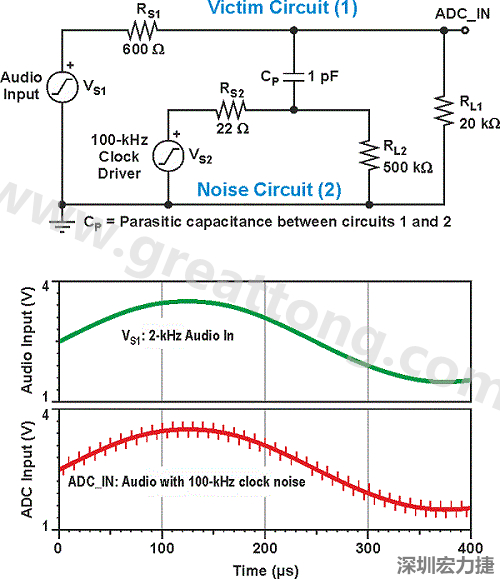

图3显示两个电路;第一个是类比数位转换器(ADC)的输入音讯电路,它包括1VP-P、2kHz正弦波(VS1)、600Ω来源阻抗(RS1)和一个20kΩ负载阻抗(RL1)。诸如600Ω的来源阻抗常见于麦克风等音讯应用,以及常见于音讯ADC的高输入阻抗(如20 k)。第二电路是驱动3.3V时脉讯号(VS2)的100 kHz时脉源,其串联终端电阻为22Ω(RS2),负载阻抗为500 kΩ(RL2)。高阻抗负载表示另一款元件的数位输入。

在实际的系统中,100~400kHz范围内的I2C串列汇流排时脉在音讯ADC和电路中很常见。虽然I2C时脉通常以突发(不连续)方式驱动,但该模拟显示在时脉驱动时可能产生的影响。在高密度音讯和资讯娱乐PCB设计中,时脉布线确实可能出现在接近灵敏的音讯走线附近。只需几个pF的寄生PCB电容就可发生电容藕合,并将时脉杂讯电流注入到受扰音讯讯号中。图3是仅使用1pF寄生电容进行的模拟示例。

图3:时脉杂讯源和音讯受扰电路

图3:时脉杂讯源和音讯受扰电路

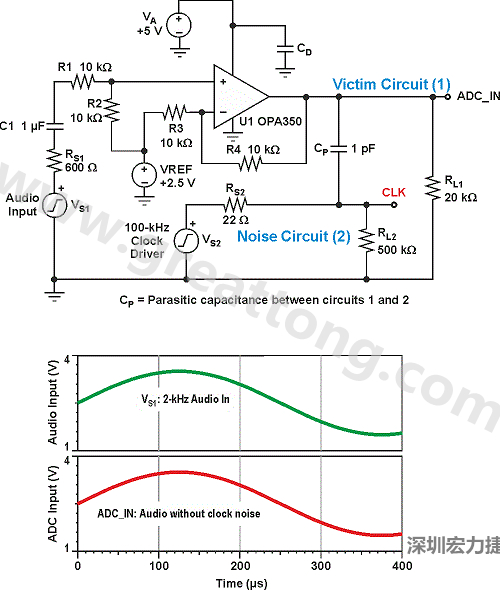

音讯电路如何降低杂讯?事实证明,降低受扰电路的阻抗是降低其对藕合杂讯敏感的一种方法。对于具有较高来源阻抗(> 50Ω)的电路,可以透过最小化与电路负载相关的来源阻抗而降低藕合杂讯。在图4中,同相配置的OPA350被添加到电路中,以缓冲讯号并隔离来源阻抗与负载。相较于600Ω,运算放大器的输出阻抗非常低,这显著降低了时脉杂讯。

图4:运算放大器电路减少来自时脉源的EMI

别忘了去藕的重要性

在电源接脚添加去藕电容,对于高频EMI杂讯的滤除以及增强运算放大器电路的抗干扰度非常有益。本文中的所有图示都显示去藕电容CD是电路的一部份。虽然探究去藕的问题会马上就会变得很复杂,但有一些适用于任何设计的理想「经验法则」。特别是选择具有以下特性的电容:

(a)极佳的温度系数,如X7R、NPO或COG;

(b)极低的等效串联电感(ESL);

(c)所需频谱范围内的最低阻抗;

(d)1~100nF范围的电容值通常都适用,但上述标淮(b)和(c)比电容值(d)更重要。

电容的布局与走线连接就像所选择的电容一样重要。尽可能地将电容放置在靠近电源接脚处。电容与PCB电源/接地的连接应尽可能短,可采用短走线或过孔连接。

结论

运算放大器有助于减少PCB上的近场EMI,并强化系统设计。以下是任何设计都必须考虑的一些要点:

? 使用精心选择的主动式滤波器配置,降低电缆/电路的输入DM杂讯(图1);

? 选择具有高CMRR的运算放大器并使用精密匹配电阻,减少电缆/电路的输入CM杂讯(图1、等式1、2);

? 选择EMI硬化元件或使用外部被动式EMI/RFI滤波器,进一步增强对于高频EMI或RFI(DM/CM杂讯)的抗干扰度(图2);

? 当驱动讯号至PCB上的其它电路时,使用运算放大器输出的低阻抗,降低藕合杂讯;

? 最后,为运算放大器和其它所有电路使用适当的去藕策略,从而降低电源杂讯。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料