对于从事高速电子设计的工程师来说,信号完整性(SI)是绕不开的话题。高速信号是指信号上升沿时间小于传输线传播时间4倍的信号,其电磁特性使得传统低速PCB布线策略不再适用。

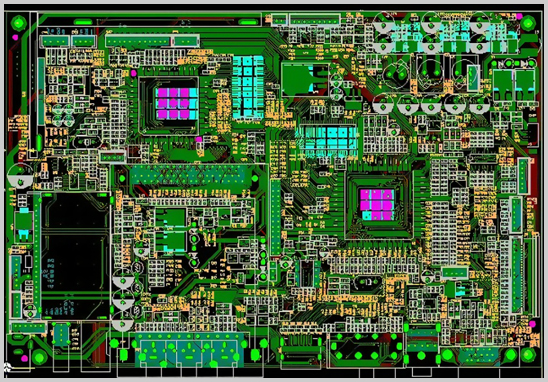

作为专业高速PCB设计公司,深圳宏力捷电子结合工程实战经验,为您整理高速PCB布线的关键规则与设计要点,帮助减少EMI问题、提升信号质量与产品可靠性。

高速PCB信号走线9大核心规则

01 屏蔽规则

高速时钟线、敏感时序线需地线屏蔽。

建议:每1000mil加一含地通孔,构建良好参考回路,抑制EMI耦合。

> 未屏蔽或局部屏蔽可能产生电磁泄漏与串扰。

02 闭环规则

避免高速线形成闭环路径,否则会产生“环形天线”,放大EMI辐射。

原则:高速线不可围绕形成闭环

03 开环规则

与闭环相反,高速走线断开形成开口,也会产生“线形天线”。

避免信号回流路径中断

04 特性阻抗连续规则

高速线过孔/跨层必须保持阻抗连续,否则会造成反射与辐射增加。

- 同层线宽一致

- 层间盲埋孔/微盲孔结构合理设计

- BGA封装过孔补偿

05 层间布线方向

相邻布线层方向应垂直,避免平行引入串扰。

推荐:横平竖直交替;

不推荐:平行走线相邻层。

06 拓扑结构规则

多负载高速网络推荐星型拓扑而非菊花链,避免反射与时序偏差。

- DDR、PCIe、SerDes等常用T-branch / Fly-by结构

07 谐振规则

布线长度避免为波长1/4倍数,防止谐振辐射。

08 去耦/旁路电容布局

高速系统必须提供最短回流路径。

原则:靠近电源引脚,环路面积最小

09 退耦电容放置规则

电容离供电引脚越近越好,优先考虑:

- 小封装

- 短回流路径

- 多级容值搭配(0.1uF + 1uF + 10uF)

|

项目 |

建议 |

|

差分线 |

同长、等距、阻抗控制、走线对称 |

|

时钟线 |

短、直、屏蔽、远离干扰源 |

|

参考地 |

大面积地层、连续参考面 |

|

过孔 |

尽量少跳层,差分对同步过孔 |

|

BGA布线 |

微盲孔、HDI结构推荐 |

为什么选择深圳宏力捷电子进行高速PCB设计?

- 20+年高速PCB设计经验

- 支持多层、高速BGA、盲埋孔HDI

- 原理图→布局走线→仿真→BOM→打样→PCBA量产

- SI、PI、EMC设计能力成熟

客户只需提供原理图,其余交给我们。

高速PCB设计不是“堆料”,而是系统设计能力与工程经验的集合。

遵循上述规则,可显著提升信号完整性、EMC能力和产品稳定性。

如需专业高速PCB设计咨询、代工服务,欢迎联系深圳宏力捷电子。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料