随着电路板复杂程度和密度的不断提高,采用示波器和逻辑分析仪对有限的测试点进行测试和除错的任务日益繁重,效率也愈加低下。新兴的EDA模拟器和波形浏览器利用上千个时域可监测信号,并能大幅增加除错范围。本文将详细介绍板级模拟技术的强大功能及其在缩短

电路板设计生产周期中的作用。

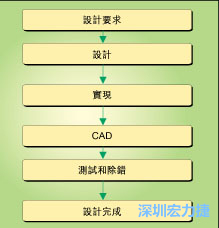

图1:典型的电路板开发流程图。

无论开发工具如何的先进,在开发的整个过程中都不可避免会出现或大或小的缺陷,它们可能潜伏在设计、实现和CAD的各个不同阶段。有缺陷并不可怕,重要的是尽早发现并消除这些缺陷,如此方能有效节省资金和时间。板级模拟工具的作用就是在电路板制造前后帮助PCB设计人员更快地开展除错工作。图1是一个典型的电路板开发流程图。

图2是在图1设计过程中增加了板级模拟的实际设计流程(这样能大幅降低板级开发成本)。

板级模拟技术

板级模拟的主要步骤如下:

a. 制定测试计划

模拟的第一步是制定完善的测试计划,该计划要充分反映产品在板级模拟方面的具体要求。测试计划可以分成二个阶段实施,阶段1为单个界面测试;阶段2为电路板的整体功能测试。

图2:板级模拟的实际设计流程。

‘阶段1’需要明确界定界面的类型和范围,并把它们完整地隔离出来,例如处理器与记忆体界面的隔离。然后做出测试案例以检查界面的连接性能和时序特性。

‘阶段2’需要将电路板划分为若干个功能块(一个功能块可以配备一个或多个界面)。每个界面藉由第一阶段确认为工作正常后,就可以把目标锁定在单个模组的功能上,即把整个电路板当成是一个黑盒子。此时可以利用合适的测试向量测试模组的详细功能,针对合成后的时序问题以及该功能块的具体数据进行处理。

b. 模拟环境的建立

在进行模拟前需要建立一个完善的模拟环境用以支援、处理和反馈各种输入信号和测量输出信号。

模拟环境要包含以下内容:1. 检查器和监视器;2. 网表;3. 模型;4. 目录结构;

1. 检查器和监视器

测试计划淮备好后要进行错误或缺陷的自动记录。把输入激励信号加到电路板上时,人们都希望得到理想的输出结果,但模拟结果可能有好有坏,这时为了分析输出结果就需要花费大量的时间。如果写下用于比较的脚本则能避免这类耗时的分析工作,另外在模拟时采用标志指示故障状态也能起到同样的效果。

在模拟时序和数据完整性问题时,我们把用于指示缺陷的任务称为监视器(monitor),而用来模拟功能特性并用于最终结果比较的脚本称为检查器(checker)。这种方法在开始时可能会花一点时间,但在实际测试阶段它能大量减少波形查找和结果分析的时间。

2. 网表

常用的原理图输入工具都具有Verilog/VHDL网表产生功能,这些网表包含所有的元件及元件之间的网络连接关系。另外,网表中的元件和埠名称均用符号来表示。

图3:好的目录结构能方便管理和跟踪所有的环境/代码文件。

3. 模型

模拟需要用到每个元件的HDL模型,标淮晶片的Verilog/VHDL模型库可以从Synopsys或其它供应商处取得。这些模型功能完全与实际元件相仿,并且能够灵活改变时序以满足最新的元件要求。如上所述,网表中的元件和埠名称与原理图输入时声明的名称是相同的,但实际模型使用的元件和埠名称可能会与网表中所用的不同。为了使网表中的埠与模型有正确的连接,需要建立一个打包文件,该文件仅仅提供网表与实际模型之间的埠映射关系,并专门为那些模型与网表中埠名称不同的元件所建。例如某元件引脚的符号名为OE_,但模型中的埠被命名为oe_n,这时就需要这样的打包文件来建立网表中符号引脚与模型埠的连接关系。

4. 目录结构

通常PCB设计者需要建立正确的目录结构用以跟踪模拟过程的输入/输出信号。这些目录可以用来区分不同类型的环境文件,这些文件类型包括了:cs、本地开发模型、监视器/检查器、脚本、板级网表、记录文件和转储文件等等。好的目录结构能够方便管理和跟踪所有的环境/代码文件。图3给出了相关的例子。

模拟案例研究

下面这个案例讨论的是一块网络数据板,它的一边是T1/E1数据线,另一边是PCI汇流排,该板的功能是完成数据从PCI汇流排到T1/E1线或T1/E1线到PCI汇流排的传输。从PCI汇流排发出的数据首先存入记忆体中,藉由本地处理器处理并转换成T1/E1讯框格式,最后藉由T1/E1线发送出去。在数据处理过程中,还有一个判别器用来切换处理器和PCI控制器对记忆体的存取。从T1/E1线接收数据再传输到PCI汇流排的过程与上述过程正好相反。本应用实例中,功能块包括:PCI汇流排控制器、裁决器和讯框器/解讯框器,如图4所示。

要将该电路板作为模拟的目标板,首先需要划出并界定各个独立界面,该案例中定义的界面有:1. CPU界面(即CPU到Flash、CPU到SDRAM、CPU到SSRAM、CPU到控制器和CPU到ROM);2. 裁决器界面;3. PCI界面;4. 讯框器/解讯框器界面。

图4:测试实例的功能块包括PCI汇流排控制器、裁决器和讯框器/解讯框器。

在界面模拟中可能存在的隐患是逻辑连接与时序问题,一旦上述各个界面的功能都藉由单独验証,就可以开展第二阶段的功能性模拟。

在第二阶段的模拟中需要定义不同的功能块,本案例有如下几种功能块:1. PCI汇流排控制器;2. 系统控制器和裁决器;3. 讯框器/解讯框器。

将讯框器/解讯框器作为模拟的功能块对象(假设PCI汇流排控制器、系统控制器和裁决器都能正常工作,要做的测试仅针对系统的讯框器/解讯框器),从PCI侧输入激励信号,在T1/E1数位线侧检查输出结果,然后再反过来做一遍。

下面是几种典型的测试情况:1. 不同数据内容的讯框;2. 讯框的时延;3. 具有不同参数设置的超讯框或扩展超讯框;4. 带CRC错误的讯框等。

可以按同样的方法模拟其它的功能块并检查模拟结果。在这一测试阶段可能会出现如下一些缺陷:1. 不同功能块中二个不同界面具有相同的网络名称,这种情况下通常会导致短路。2. 系统综合问题,如信号走线从一个界面跳到了另外一个界面。3. 某个界面的数据格式不能被其它界面所支援。该阶段也称为电路板的数据通道模拟。

模拟技巧

下面是板级模拟的一些技巧:1. 对于可程式元件要尽量利用后向标注文件。这些文件包含有可预测的输入输出信号时序资讯;2. 检查网表中所有的电源网络说明,如果有任何遗漏应立即补齐;3. 最终网表中存在的但不会被黏着到电路板上的元件需要加以注明。

虽然功能性模拟具有以上一些突出优点,但也有一定的局限性,使得模拟结果不能完全类比实际的电路板,这种局限性表现在:1. 缺少不同的电源网络标识,因为在HDL中虽然可以声明电源网络但不能标明具体数值,如5V还是3.3V。目前版本的HDL尚不支援这一功能。2. HDL不能模拟类比界面。3. 这种模拟不能发现与驱动能力有关的问题。4. 执行记忆体测试需要巨大的转储文件和较长的执行时间。

本文结论

板级模拟是发现板级设计缺陷的一种直接有效的途径,虽然需要少量的模拟开销,但它能大幅缩短产品上市时间并且有效地降低产品成本。今天,逻辑电路变得越来越复杂、板的物理尺寸越来越小,新产品上市时间愈加紧迫,因而板级模拟技术尤其显得重要。当然需要提醒大家的是,再好的模拟也不能完全替代实验室的物理测试过程。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料